新聞資訊

新聞資訊 知識專欄

知識專欄寬禁帶半導體如硅碳化物的出現(xiàn)顯著提高了電源器件的性能,使其能夠在更高電壓下運行,降低損耗,并提高功率和電流密度。然而,這些進展也要求更高效且具有成本效益的封裝解決方案,以匹配下一代器件的增強熱和電性能。

同時,新興應用,特別是電動汽車和車載充電器,對長期可靠性、緊湊的形狀和高熱耐久性提出了嚴格的要求。為應對這些挑戰(zhàn),先進的封裝和組裝技術,如扇出面板級封裝(FOPLP),已經被積極探索。結合納米燒結銅(Cu)芯片附加技術,這些技術為提高高電壓硅碳化物模塊的熱管理、機械穩(wěn)健性和電性能提供了有希望的路徑。

什么是扇出?

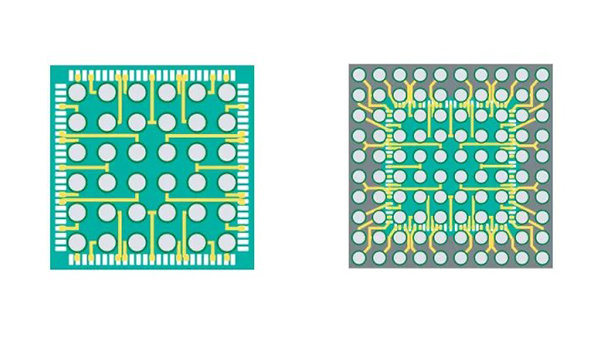

“扇出”的核心是將輸入/輸出連接從裸半導體芯片的小占地面積重新分配到其邊緣外部的更大區(qū)域。在傳統(tǒng)的“扇入”封裝中,輸入/輸出焊盤被限制在芯片內部。隨著芯片集成更多功能并需要更多連接,這種方法變得有限(見圖1)。

扇出封裝通過向外重新分配輸入/輸出連接,允許更多的外部連接和更小的間距。典型的過程包括:

將單個或多個芯片重構到較大的載體基板上——無論是晶圓還是在FOPLP中使用的矩形面板。芯片被精確放置,并根據(jù)要構建的功能單元進行分組(例如,半橋模塊)。

在芯片之間分配間距以啟用互連路由。

用環(huán)氧模塑材料進行封裝,形成平坦且均勻的表面。

在模塑表面上形成重分布層(RDL)。該層包含細金屬電路,重新路由芯片的內部焊盤到更大的區(qū)域。RDL取代傳統(tǒng)的焊線,降低寄生電感,并增強高頻性能。該概念在圖1中有示意。

將焊球或焊點添加到RDL以實現(xiàn)PCB級集成。

什么是面板級封裝?

面板級封裝是一種先進的組裝方法,其中芯片被封裝在大型矩形面板上,而不是用于晶圓級封裝的圓形硅晶圓。常見的面板尺寸包括510 × 515 mm和600 × 600 mm,提供:

更高的通量,意味著每個面板可以處理更多芯片

更低的單位成本,改善材料利用率和面板效率

可擴展性,適合于汽車、消費和工業(yè)領域的大規(guī)模生產

FOPLP的一個關鍵優(yōu)勢是其與標準PCB行業(yè)工具的兼容性,這些工具經過優(yōu)化以處理大型矩形基板。這減少了資本投資,避免了完全新的晶圓級工具的需求——特別是在晶圓尺寸的可擴展性達到實際限制時。

燒結銅芯片附加

在2025年IEEE第75屆電子組件與技術會議上提出的一項研究介紹了納米燒結銅芯片附加作為提高硅碳化物FOPLP模塊性能的解決方案。在中國國家自然科學基金的支持下,該工作標志著納米燒結銅在高電壓應用的FOPLP中首次成功集成。

基于銅的FOPLP使用凹陷的部分空心引線框設計,硅碳化物芯片通過納米燒結銅直接安裝。這消除了額外銅連接器的需求,因為芯片表面與引線框平齊,簡化了垂直集成和路由。

在基線銀(Ag)基礎設計中,明確使用了銅連接器以實現(xiàn)磁通抵消——一種相對電流回路最小化雜散電感和電磁干擾的排列。在優(yōu)化的銅燒結版本中,芯片到引線框的布局自然而然地支持磁通抵消,以較低的復雜性、高度和材料使用實現(xiàn)類似的電氣益處。

納米燒結過程概述

納米燒結使用銅納米顆粒在芯片與基板之間形成密集的熱導電連接。在FOPLP中,這種方法相較于基于焊料的附加具有顯著優(yōu)勢:

將由銅納米顆粒組成的漿料或油墨沉積在引線框腔或芯片背面。

將芯片放置并進行熱燒結(約200°C至300°C),在此過程中納米顆粒在不熔化的情況下融合,形成密集的互連。

這種方法確保了高熱導率、低連接空隙率,并與薄型高功率FOPLP模塊兼容——這對硅碳化物mosfet在緊湊布局中的可靠運行至關重要。

使用的硅碳化物MOSFET

在研究中使用的硅碳化物MOSFET由SIChain Semiconductor提供,具有1200 V、80 A和40 mΩ的規(guī)格。芯片尺寸為4.134 × 3.74 mm2,厚度為0.2 mm。柵極和源極用Ni/Pd/Au鍍層,漏極則使用Ti/Ni/Ag。所用面板基板為508 × 203 mm2。

熱機械仿真

通過全面的有限元仿真評估了芯片附加材料和封裝基板設計對FOPLP性能的影響。為了驗證熱性能,進行了穩(wěn)態(tài)熱阻測試。隨后進行了熱機械虛擬原型設計,以評估在操作和循環(huán)條件下的結構完整性。此外,使用Ansys Q3D 2021仿真工具提取寄生電感,并分析開關頻率對電性能的影響。

兩種仿真封裝——銀粘合劑(FOPLP-Ag)和納米燒結銅(FOPLP-Cu)——共享相同的內部架構和總體尺寸。除了芯片附加材料外,其他所有組件,包括散熱片墊、RDL、連接器和引線框,均由銅制成。

在25°C的環(huán)境溫度下,以58.5 W的施加功率(對應于ID = 40 A,VDS = 1.46 V,VGS = 15 V)進行的穩(wěn)態(tài)熱仿真。散熱片和焊接墊均固定在25°C,以實現(xiàn)雙面冷卻。

在兩種封裝變體中,硅碳化物芯片的溫度分布用于使用以下公式計算熱阻(R):

R = (Tj ? Tamb) ÷ P

其中Tj是結溫,Tamb是環(huán)境溫度,P是功耗。

不同冷卻條件下的熱阻仿真結果總結在表1中。

雙面冷卻的熱阻為FOPLP-Ag的0.24°C/W和FOPLP-Cu的0.14°C/W。燒結銅版本顯示出比銀粘合劑更好的熱導率。

熱機械應力

芯片溫度的上升由于熱膨脹系數(shù)的不匹配而產生機械應力。這可能導致界面分層或開裂。

在雙面冷卻下:

FOPLP-Ag:最大應力 = 37.9 MPa,變形 = 1.4 × 10?6米FOPLP-Cu:最大應力 = 25.6 MPa,變形 = 8.3 × 10?7米

在兩種情況下,最大應力和變形均發(fā)生在芯片表面和封裝的角落。

在熱循環(huán)(25°C → 320°C)下:

FOPLP-Ag:最大應力 = 189 MPa,變形 = 1.0 × 10?4米FOPLP-Cu:最大應力 = 190 MPa,變形 = 9.1 × 10?5米

銅版本的應力略高,歸因于其更高的彈性模量,盡管變形保持較低。

仿真和實驗證明FOPLP-Cu在熱和電性能上優(yōu)于基于銀的版本。其好處包括:

較低的寄生電感

減少的機械變形

增強的熱散逸

穩(wěn)健的機械界面

驗證測試確認了所提出的FOPLP-Cu設計的可行性和可靠性,未觀察到分層現(xiàn)象。電氣特性(靜態(tài)、開關和熱阻)驗證了正常功能。

這項工作證明了基于硅碳化物的FOPLP通過納米燒結銅增強的潛力,適用于小型化、高效率和熱穩(wěn)健的電源模塊,為其在汽車和工業(yè)領域的商業(yè)規(guī)模部署鋪平了道路。