新聞資訊

新聞資訊 知識專欄

知識專欄本文深度解析電子元器件20+主流封裝技術(shù),涵蓋DIP、SOP、QFP、BGA等封裝特點、應(yīng)用場景及選型建議,助工程師高效匹配設(shè)計方案。

一、為什么封裝技術(shù)是電子設(shè)計的核心?

在電子元器件領(lǐng)域,封裝不僅是芯片的“保護(hù)殼”,更是連接設(shè)計與制造的橋梁。封裝形式直接影響電路板的布局密度、散熱性能、信號傳輸效率和成本控制。據(jù)統(tǒng)計,60%以上的硬件失效案例與封裝選型不當(dāng)直接相關(guān)。掌握主流封裝技術(shù),是工程師提升產(chǎn)品可靠性的關(guān)鍵一步。

二、四大類封裝技術(shù)詳解(附典型型號)

1. 引腳插入型(Through-Hole)

DIP(雙列直插封裝)

結(jié)構(gòu):兩排平行引腳,間距2.54mm

優(yōu)勢:手工焊接方便,抗機械應(yīng)力強

應(yīng)用:51單片機、傳統(tǒng)邏輯芯片(如74系列)

PGA(針柵陣列封裝)

特點:底部密布針狀引腳,適合高頻CPU

代表型號:Intel 80486處理器

2. 表面貼裝型(SMT)

SOP/SOIC(小外形封裝)

引腳數(shù):8-48pin,引腳間距1.27mm

場景:存儲器(24C02 EEPROM)、運放(LM358)

QFP(四方扁平封裝)

進(jìn)階型號:TQFP(薄型)、LQFP(低剖面)

典型應(yīng)用:STM32系列MCU

3. 高密度封裝

BGA(球柵陣列封裝)

創(chuàng)新點:底部錫球替代引腳,間距0.5-1.0mm

優(yōu)勢:提升40%布線密度,高頻性能優(yōu)異

案例:手機處理器(驍龍系列)、FPGA芯片

QFN(無引腳方形封裝)

散熱設(shè)計:底部裸露焊盤直連PCB散熱層

適用場景:功率器件(如TI的TPS系列電源芯片)

4. 特殊功能封裝

SIP(系統(tǒng)級封裝)

技術(shù)突破:集成多個芯片于單一封裝,縮短信號路徑

應(yīng)用:智能手表模組、射頻前端模塊

Flip-Chip(倒裝焊)

工藝特點:芯片倒置,通過凸點直接連接基板

優(yōu)勢:降低30%信號延遲

三、工程師必看的封裝選型5大原則

空間限制

可穿戴設(shè)備優(yōu)選CSP(芯片級封裝),尺寸可縮小至芯片的1.2倍

工業(yè)控制板可選用DIP或SOP降低成本

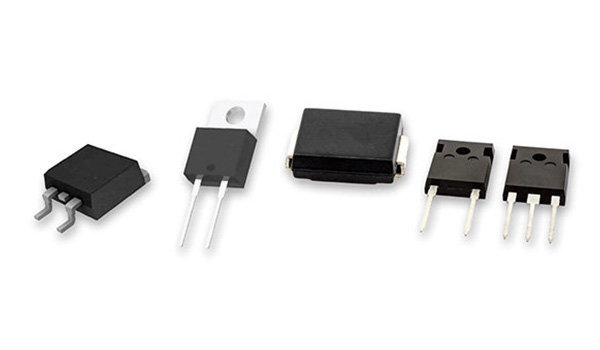

散熱需求

功率超過5W的器件建議選擇TO-220/TO-263封裝

QFN底部散熱焊盤需搭配4層以上PCB

成本控制

消費類產(chǎn)品優(yōu)先SMT封裝(比DIP節(jié)約15%組裝成本)

小批量研發(fā)可用模塊化封裝(如ESP32-WROOM)

生產(chǎn)工藝

BGA需X光檢測設(shè)備,中小工廠慎選

0.4mm以下引腳間距建議采用半自動貼片機

供應(yīng)鏈考量

冷門封裝(如CPGA)交期可能長達(dá)12周

優(yōu)選JEDEC標(biāo)準(zhǔn)封裝,替代方案更多

浮思特科技專注功率器件領(lǐng)域,為客戶提供IGBT、IPM模塊等功率器件以及MCU和觸控芯片,是一家擁有核心技術(shù)的電子元器件供應(yīng)商和解決方案商。