新聞資訊

新聞資訊 知識專欄

知識專欄 長期以來,Lattice

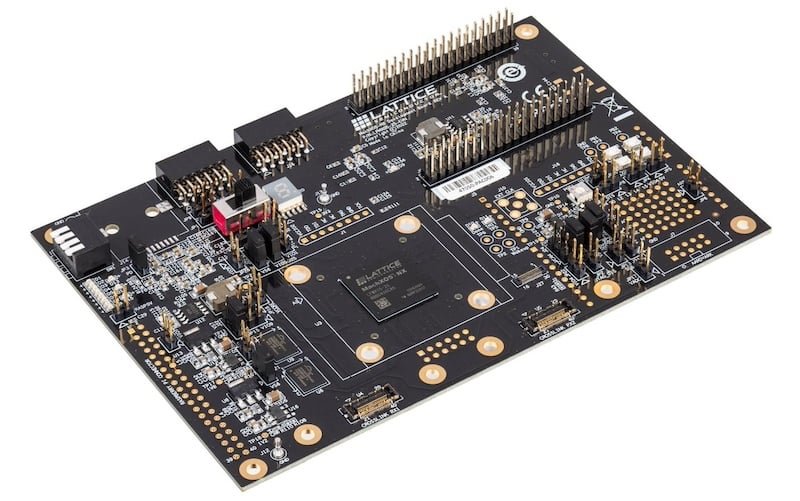

Semiconductor一直是低功耗、低成本FPGA行業的重要參與者,最近發布了MachXO5D-NX系列。這一中檔系列將低成本、低功耗與廣泛的外圍設備和安全功能相結合,使其適用于安全邊緣設備。

FPGA的可編程性自身帶來了獨特的安全挑戰和機遇。雖然現場可編程性可能成為不法分子的入口,但也使制造商有機會在部署后對安全性進行調整和更新。

Lattice設計了MachXO5D-NX系列先進的安全控制FPGA,配備了一套內置的硬件加密和安全功能。這使得該系列具備了固定硬件的安全性和FPGA的靈活性。通過片上Flash和硬件加密,FPGA線可以使用更少的芯片構建,從而防止了在加載時的代碼捕獲。

三芯片MachXO5D-NX系列

該三芯片系列具有一系列邏輯單元:

FMXO5-25:27000個邏輯單元

LFMXO5-55T:53000個邏輯單元

LFMXO5-100T:96000個邏輯單元

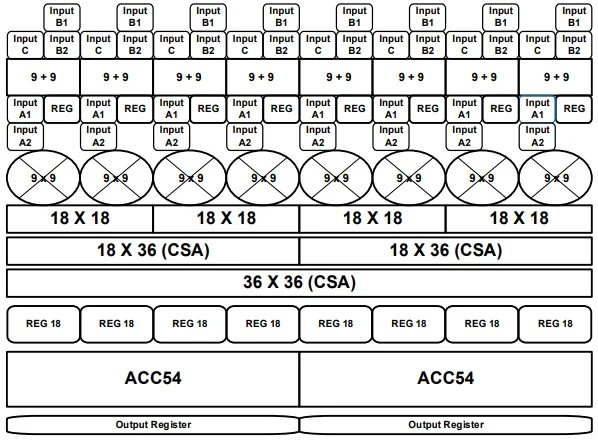

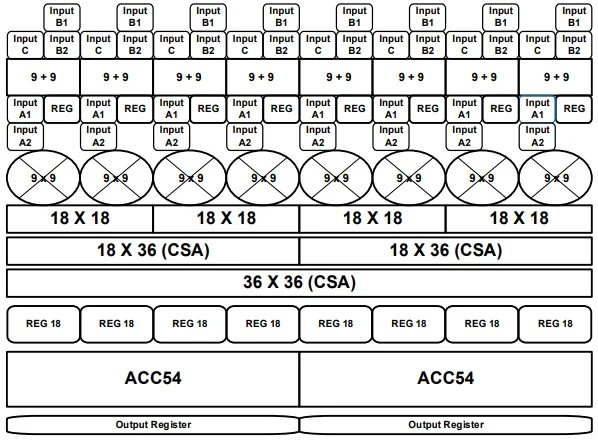

該系列的其他特點包括20至156個SysDSP 18x18乘法器和1.9 Mb至7.3 Mb的嵌入式RAM,形式為EBR或LRAM。此外,該系列還具有200至300個高性能、寬范圍和多電壓I/O。

乘法器和DSP單元可以實現邊緣AI或其他數學密集型應用。它們配備了一系列內置的外圍設備,包括MIPI D-PHY(CSI-2、DSI)、LVDS、SLVS、subLVDS、千兆以太網和PCIe(Gen1和Gen2)。芯片具有片上嵌入式Flash存儲器、多重啟動和用戶Flash存儲器(UFM)。除了片上分布式RAM、EBR和LRAM內存塊外,芯片還具有用于DDR3、DDR3L和LPDDR4的高達1066 Mbps的內置接口。

這些芯片由Lattice Radiant設計套件和流行設計工具的綜合庫支持。Lattice擁有大量預先設計的軟核和標準化IP模塊庫,可供新的FPGA系列使用。

信任根和其他安全功能

信任根(RoT)是芯片上包含加密功能密鑰的安全區域。MachXO5D-NX系列成員配備了一款硬件加密引擎,支持先進的加密標準(AES)、哈希算法和真隨機數發生器(TRNG)。每個成員都包括一個用于保護設備身份的獨特秘密標識(USID)。

這些設備具備加密敏捷性,意味著它們可以在多種加密算法或方法之間切換。這些芯片支持商用國家安全算法(CNSA),用于比特流和用戶數據保護。支持的標準包括AES-256、ECDSA-384/521、SHA2-256,384/512和RSA 3072/4096。

將加密和解密功能集成到FPGA中是一種常見的設計特征。然而,通過在硬件硅中加入保護,不需要將FPGA結構專門用于幾乎所有應用都應該具備的安全功能。

Lattice Nexus平臺建立在低功耗28納米全耗盡硅-絕緣體(FD-SOI)工藝上。FD-SOI通過在埋藏絕緣體上方放置超薄硅層來減少漏電流。分層結構減少了襯底體積,并消除了溝道摻雜的必要,從而創造出全耗盡晶體管。這一工藝使Lattice零件的功耗降低了75%,軟錯誤率下降了100倍。低軟錯誤率意味著在電氣噪聲和輻射環境中對單事件故障(SEU)有更高可靠性的產品。

除了低軟錯誤率之外,這些芯片還具有固定硬件軟錯誤檢測(SED)電路,用于檢測和修復SRAM錯誤。這一設計改進了以前的Lattice FPGA SED實現,并具有兩層SED以提高可靠性。

浮思特科技專注功率器件領域,為客戶提供IGBT、IPM模塊等功率器件以及MCU和觸控芯片,是一家擁有核心技術的電子元器件供應商和解決方案商。