新聞資訊

新聞資訊 知識專欄

知識專欄 自20世紀90年代初推出首批商用單晶SIC晶片以來,其組成未曾改變,僅隨著時間的推移改變了直徑并降低了缺陷率。SmartSiC是一種基于新范式的工程基板,它在一個基板上結(jié)合了高質(zhì)量的單晶SiC頂層和高度電導(dǎo)的聚晶SiC支撐晶片,從而在器件性能和可靠性方面實現(xiàn)了前所未有的提升。

在電力電子領(lǐng)域,碳化硅(SiC)技術(shù)對于推動向電動移動性的轉(zhuǎn)變和提高可再生能源系統(tǒng)的效率至關(guān)重要。隨著市場需求的增加,功率半導(dǎo)體公司面臨著迅速擴大生產(chǎn)能力的壓力。盡管4H-SiC材料的質(zhì)量和可用性有了顯著提升,但生產(chǎn)低缺陷密度和高性能SiC晶片以實現(xiàn)最佳產(chǎn)量的挑戰(zhàn)依然存在。

為了應(yīng)對這一緊迫需求,一種開創(chuàng)性的SiC工程基板被引入以滿足行業(yè)需求。2023年9月,一條專用制造線的揭幕標志著重要里程碑,預(yù)示著這種創(chuàng)新SiC基板的大規(guī)模生產(chǎn)開始。這一戰(zhàn)略舉措有望徹底改變SiC技術(shù)的格局,為當(dāng)前制造限制提供突破性解決方案,并為電力電子應(yīng)用的效率和性能提升鋪平道路。

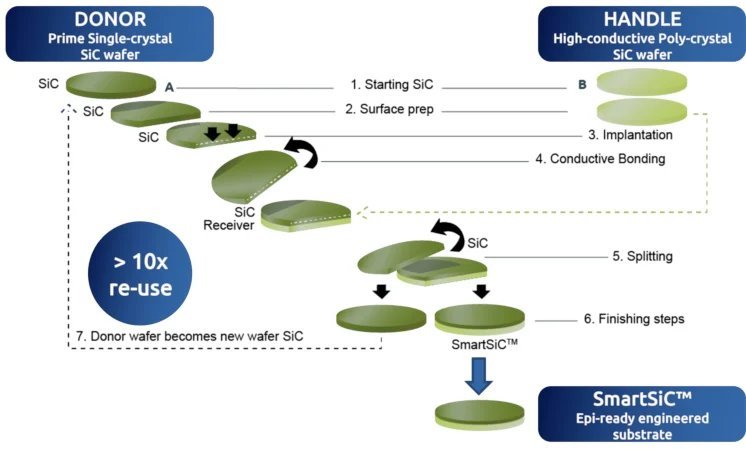

SmartSiC基板的制造依賴于Smart Cut技術(shù),并在SiC器件制造中提供了顯著優(yōu)勢。以下是其關(guān)鍵特性和益處的分解:

高質(zhì)量SiC頂層:Smart Cut技術(shù)促進了高質(zhì)量SiC層在支撐晶片上的轉(zhuǎn)移,作為漂移外延生長的種子。這一過程對于優(yōu)化器件產(chǎn)量和可靠性至關(guān)重要,確保最終器件符合嚴格的質(zhì)量標準。

低電阻率支撐晶片:該技術(shù)采用低電阻率支撐晶片,典型電阻率為2 mOhm.cm(標準SiC材料電阻率約為20 mOhm.cm)。這一特性增強了器件導(dǎo)電性,同時實現(xiàn)了開關(guān)損耗的最小化,最終提高了基于SiC器件的應(yīng)用的整體性能。

兼容不同晶片直徑:Smart Cut技術(shù)兼容任何基板直徑,適用于150 mm和200 mm晶片。

基于上述特性,獲得的SmartSiC工程基板由亞微米厚(400至800 nm)的高質(zhì)量單晶4H-SiC頂層和聚晶SiC支撐晶片組成。最終工程基板的厚度為150 mm晶片350 μm,200 mm晶片500 μm。這種組成確保了基板的結(jié)構(gòu)完整性和性能,有助于SiC器件的可靠性和效率。

此外,通過使初始單晶供體晶片的可重復(fù)使用性成為可能,SmartSiC技術(shù)提供了對難以實現(xiàn)的SiC晶錠的最有效利用。與通常每晶錠最多提取50片晶片的傳統(tǒng)SiC材料加工相比,Smart Cut技術(shù)可以從同一晶錠準備多達500個工程基板。這種生產(chǎn)力的顯著提高代表了SiC器件制造的成本節(jié)約和資源高效解決方案。

圖1

應(yīng)用于SmartSiC工程基板制造的Smart Cut過程如圖1所示。

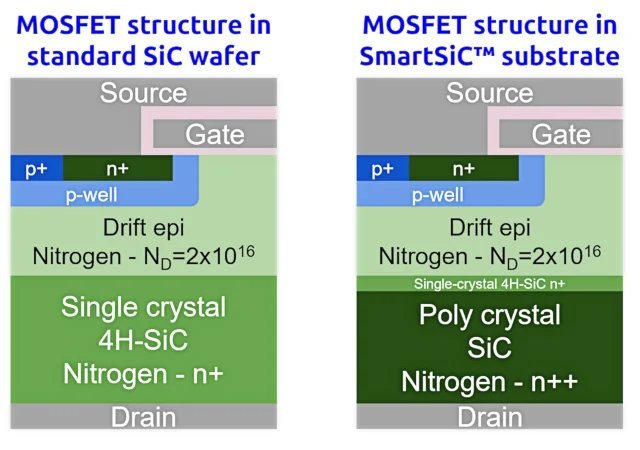

為了研究SmartSiC工程基板與標準單晶4H-SiC晶片的優(yōu)點,在兩種基板上制造了n型、13 mOhm/650 V Gen2平面SiC MOSFET,并作為單一批次同時處理。

作為參考的單晶4H-SiC晶片是氮摻雜的,典型電阻率為20 mOhm.cm,而SmartSiC基板的聚晶SiC支撐晶片具有更高的氮摻雜和典型電阻率為2 mOhm.cm。漂移外延是氮摻雜的,摻雜濃度ND≈2x1016cm-3。磷和鋁注入分別用于形成源極和體區(qū)域。柵氧化層是55nm厚的SiO2層,而高摻雜n型聚晶Si用作柵極電極。標準單晶SiC晶片和SmartSiC?基板上的測試車輛MOSFET結(jié)構(gòu)如圖2所示。

圖2

結(jié)果

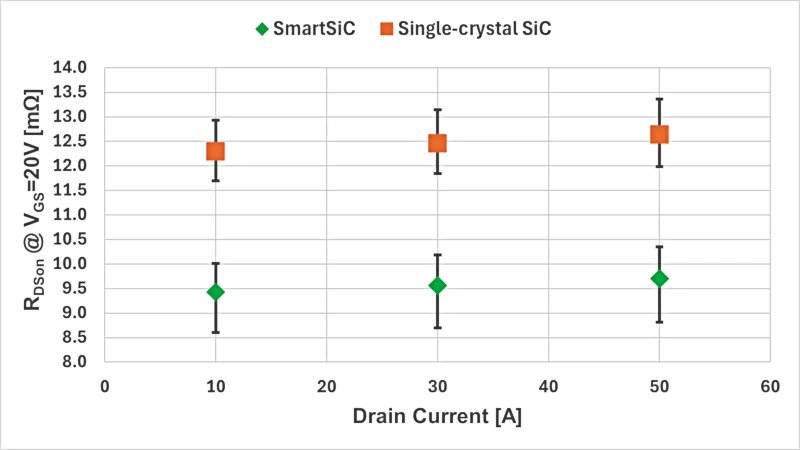

這里展示了在13 mOhm 650 V Gen2平面SiC MOSFET上獲得的結(jié)果。

圖3展示了器件的RDSon比較。結(jié)果顯示,與SmartSiC基板相比,導(dǎo)通電阻平均降低了約24%。這一改進是由于SmartSiC基板的聚晶SiC支撐晶片的電阻率遠低,以及其能夠?qū)崿F(xiàn)更低電阻率金屬接觸(在這種情況下是背面漏極接觸)的能力。

圖3

如此強烈的RDSon降低(約24%)接近于從一代器件過渡到下一代時可以預(yù)期的水平。

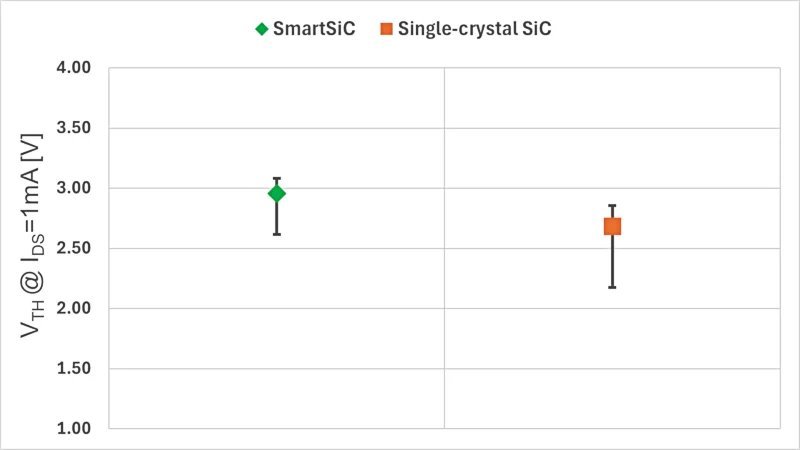

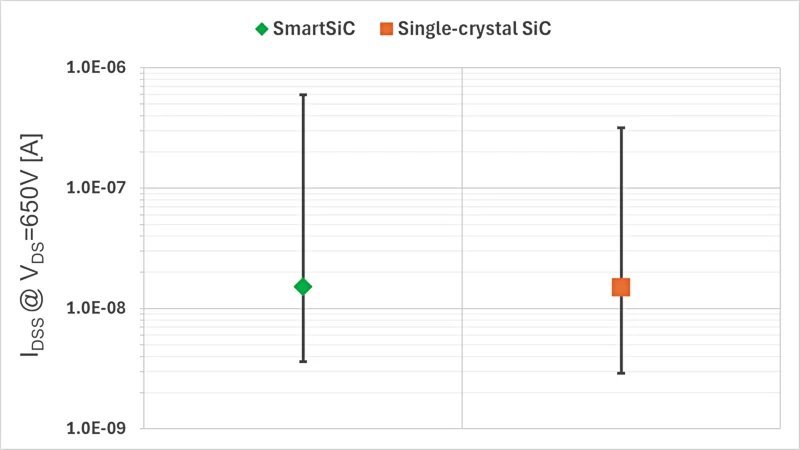

圖4和圖5分別展示了在單晶SiC晶片和SmartSiC基板上制造的同一器件的閾值電壓和漏電流。結(jié)果顯示,這兩種基板在這些參數(shù)上表現(xiàn)出等效行為。

圖4

圖5

其他器件的潛力

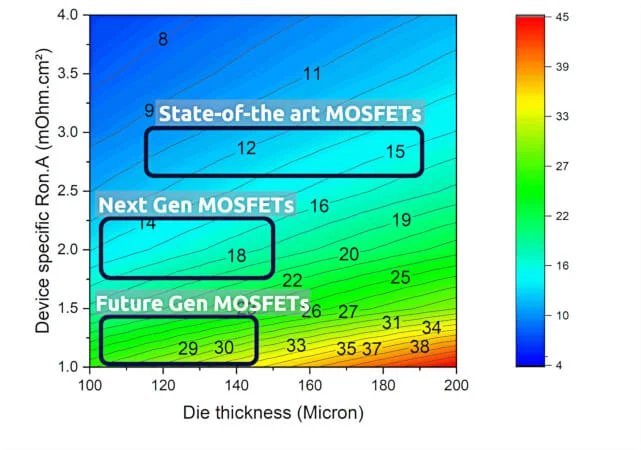

如前所述,與電阻率約為20 mOhm.cm的標準單晶SiC基板相比,聚晶SiC材料可以實現(xiàn)低至1 mOhm.cm的電阻率,典型值約為2 mOhm.cm。此外,聚晶SiC的高摻雜水平有助于將接觸電阻降低至遠低于10 μOhm.cm2。這些特性使SmartSiC基板能夠提高器件的電流密度,從而允許減小MOSFET和二極管的器件尺寸。

特別是對于FET,盡管總增益取決于初始器件特定電阻(Ron.A)和晶片厚度,但圖6顯示,F(xiàn)ET技術(shù)越先進,獲得的增益越高。我們所說的初始Ron.A是指器件在單晶SiC晶片上制造時的電阻。例如,對于初始Ron.A為2.8 mOhm.cm2和晶片厚度為180μm的FET,圖5顯示,在SmartSiC基板上制造時,新的Ron.A降低了15%(增益為15%)。請注意,這種增益與器件的電壓等級無關(guān)。

前一段中提到的2.8 mOhm.cm2值對應(yīng)于當(dāng)前1200 V SiC MOSFET的先進水平。然而,當(dāng)考慮到未來幾年的器件代數(shù)時,預(yù)計Ron.A增益(減少)將超過20%,始終呈現(xiàn)出使用SmartSiC工程基板的優(yōu)勢,即“至少”多一代的優(yōu)勢。

極端增益情況出現(xiàn)在當(dāng)今最先進的JFET中,這是400 V和800 V電動汽車固態(tài)斷路器的首選。以750 V SiC JFET為例,初始Ron.A約為0.7 mOhm.cm2,預(yù)計增益約為30%。

圖6

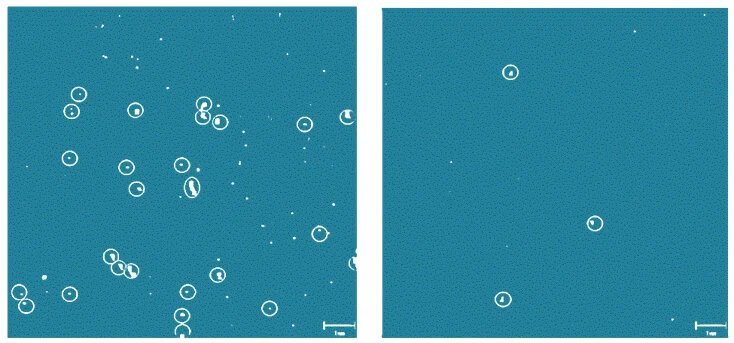

最后但同樣重要的是,初步分析顯示,SmartSiC工程基板在特定電評估中進一步證實了其對雙極退化的寶貴魯棒性。這種退化現(xiàn)象出現(xiàn)在SiC基板上,是由于在暴露于高雙極電流(由于電子和空穴同時存在)時,SiC晶體內(nèi)的基平面位錯(BPD)的滑動(擴展)。這通常發(fā)生在SiC MOSFET的反向?qū)ㄆ陂g,電流通過晶體管的PiN型體二極管。

為了驗證這種魯棒性,外延標準單晶SiC晶片和SmartSiC基板暴露于旨在揭示雙極退化的應(yīng)力條件下。這是通過使用ITES公司開發(fā)的E-V-C技術(shù)進行的。經(jīng)過應(yīng)力測試后,結(jié)果顯示,與標準SiC晶片獲得的結(jié)果相比,SmartSiC情況下的肖克利堆垛故障數(shù)量及其典型尺寸較低。結(jié)果表明,SmartSiC設(shè)計在抗雙極退化方面具有固有的優(yōu)勢。這一特性之前通過在受到質(zhì)子輻照的4H-SiC外延層上進行的正向電流應(yīng)力測試進行了評估。

未來代數(shù)

在當(dāng)前加速部署SiC器件以實現(xiàn)移動性和電力轉(zhuǎn)換行業(yè)脫碳的背景下,SmartSiC提供了無與倫比的特性,允許更高的功率密度和更可靠的應(yīng)用。

圖7

從在單晶SiC晶片和SmartSiC基板上制造的MOSFET獲得的結(jié)果顯示,后者提供的增益相當(dāng)于從一代器件過渡到下一代時獲得的增益。

在當(dāng)前可用的器件代數(shù)上驗證的增益顯示,SmartSiC的優(yōu)勢在未來的器件代數(shù)中將更加明顯,以及在Ron.A低得多的其他器件(如JFET)中。

浮思特科技專注功率器件領(lǐng)域,為客戶提供IGBT、IPM模塊等功率器件以及MCU和觸控芯片,是一家擁有核心技術(shù)的電子元器件供應(yīng)商和解決方案商。