新聞資訊

新聞資訊 知識專欄

知識專欄 在之前的文章中,我解釋了如何獲取集成電路mosfet的高級SPICE模型,并將其整合到LTspice模擬中。隨后,我們利用這個模型研究了NMOS晶體管的閾值電壓。本文中,我們將使用相同的模型來生成圖表,直觀地展示晶體管的電氣行為。

繪制漏極電流與漏源電壓的關系

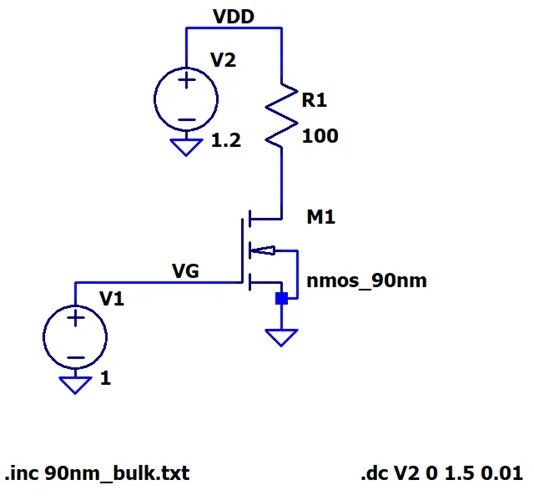

我們將首先制作一個基本的漏極電流(ID)與漏源電壓(VDS)的關系圖。為此,我們將柵極電壓設定為一個遠高于閾值電壓的固定值,然后進行一個直流掃描模擬,其中VDD的值逐漸增加。圖1展示了我們將使用的電路圖。

圖1

柵源電壓(VGS)為1V,遠高于我們在前一篇文章中通過模擬找到的320mV閾值電壓。同時,圖1右下角的.dc模擬命令告訴LTspice執行兩項操作:

將V2源(VDD)從0V增加到1.5V,增量為0.01V。

使用這一系列的VDD值作為自變量。

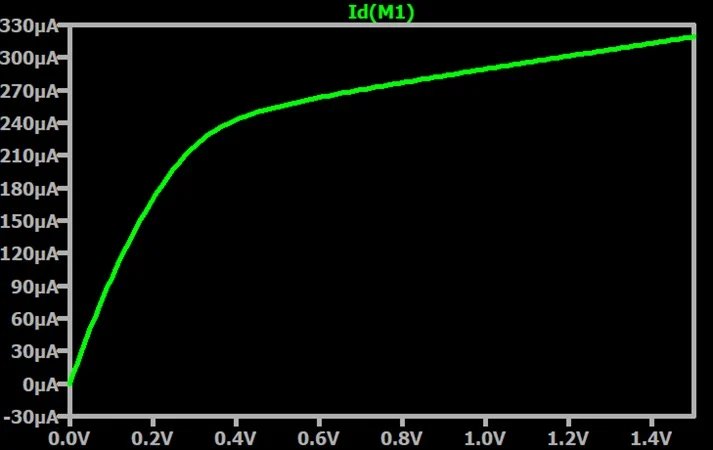

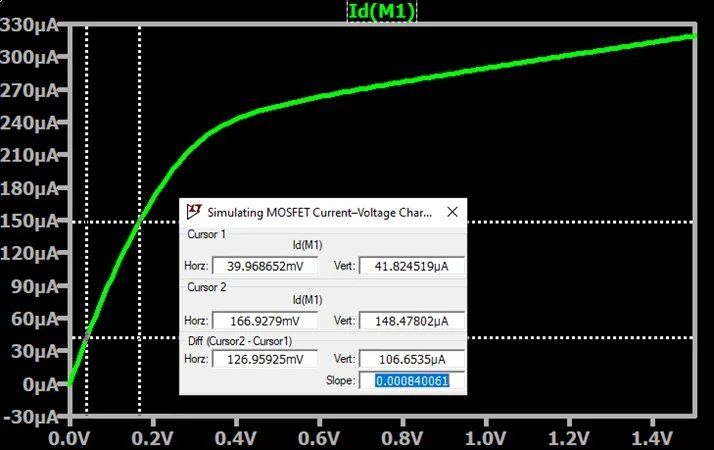

模擬結果如圖2所示。

圖2

柵極電壓足夠高,使得導通成為可能,因此一旦VDS超過零,電流就開始流動。在較低的漏極電壓下,漏極電流隨著VDS的線性增加而線性增加。然而,漏極電流在大約0.4V時開始趨于平穩,之后增加得更慢。這種從圖表的高斜率部分到低斜率部分的過渡對應于從FET的線性區域到飽和區域的過渡。

當漏極電壓較低時,柵極電壓打開一個從漏極延伸到源極的通道,電流更自由地通過FET的通道流動。隨著漏極電壓接近過驅動電壓,漏極處的通道被夾斷,電流不再像以前那樣自由流動。過驅動電壓等于柵極電壓減去閾值電壓。

測量線性區域的電阻

在線性區域,NMOS的行為類似于電壓控制的電阻器。這就是該區域得名的原因——當電流通過普通電阻時,電壓和電流之間的關系是線性的。如果我們查看歐姆定律,這一點很明顯:

如果我們用許多人在高中代數中使用的字母替換V、I和R,歐姆定律變為:

其中:

y,垂直軸,代表電壓 x,水平軸,代表電流 m,繪制線的斜率,代表電阻。

為了確定這個NMOS晶體管在線性區域的電阻,我們只需要找到m。由于我們在圖2中繪制了漏極電流和漏極電壓之間的關系,我們已經在一定程度上完成了這一步。然而,我們在y軸上繪制了電流,在x軸上繪制了電壓——為了使V = IR成立,電壓必須是y值,電流必須是x值。m不是圖2中線的斜率,而是斜率的倒數。

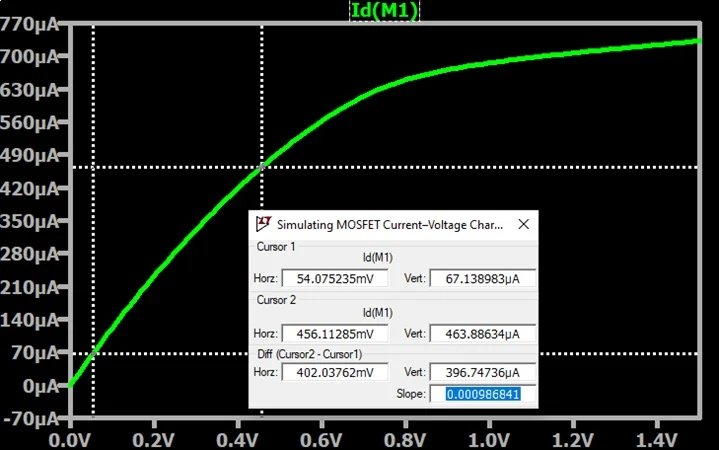

這只需要多加一步。我們使用LTspice找到斜率(圖3),然后取其倒數。

圖3

線的斜率為0.00084。因此,總電阻為1/0.00084 = 1190Ω。這個總電阻包括一個100Ω的漏極電阻,使得NMOS的通道電阻等于1090Ω。

更高的柵源電壓使得通道更具導電性,因此如果我們增加柵極電壓,我們可以預期這個電阻會降低。圖4展示了如果我將柵極電壓增加到2V會發生什么。

圖4

當VGS = 2V時,斜率等于0.00099。取這個值的倒數,我們得到1010Ω。一旦我們減去100Ω的漏極電阻,FET在線性區域的通道電阻為910Ω。這比我們之前的電阻值減少了180Ω,因此我們可以認為我們的預期得到了證實。

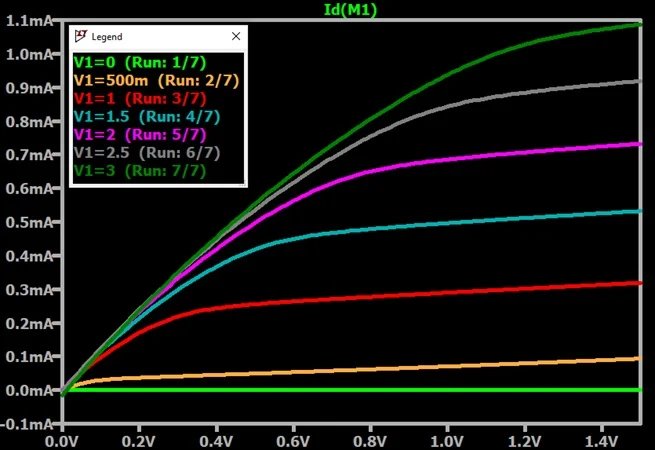

生成一組特性曲線

關于FET行為的討論通常伴隨著一個漏極電流與漏極電壓的圖表,其中包含多條曲線來代表不同柵源電壓的結果。這使得單個圖表能夠傳達大量關于柵源電壓、漏源電壓和漏極電流之間電氣關系的信息。

為了在LTspice中生成這種類型的圖表,我們只需要修改模擬命令,使其指定對V2和V1(即柵極電壓)進行掃描。新的模擬命令是:

V2的掃描與之前相同,但我們添加了文本,告訴LTspice將V1源從0V增加到3V,增量為0.5V。結果是圖5中的多色圖。

圖5

為了使您的圖表顯示像圖5那樣的圖例,只需按照以下步驟操作:

右鍵單擊圖表窗口。

轉到視圖。

選擇步長圖例。

總結

SPICE模擬是深入了解MOSFET并研究微妙電氣細節或復雜電路實現的好方法,浮思特科技專注功率器件領域,為客戶提供IGBT、IPM模塊等功率器件以及MCU和觸控芯片,是一家擁有核心技術的電子元器件供應商和解決方案商。