新聞資訊

新聞資訊 知識專欄

知識專欄 隨著對越來越小、功耗更低的電子設備需求的增長,低功耗芯片設計已經成為一個基本角色。人工智能在嵌入式系統中的日益普及,正挑戰著低功耗芯片設計師們去融入更高密度、更具創新性的架構和制造工藝。為了滿足AI芯片在功能性、可制造性、成本和可靠性方面的要求,合適的功率分析技術和工具是必要的。

低功耗設計

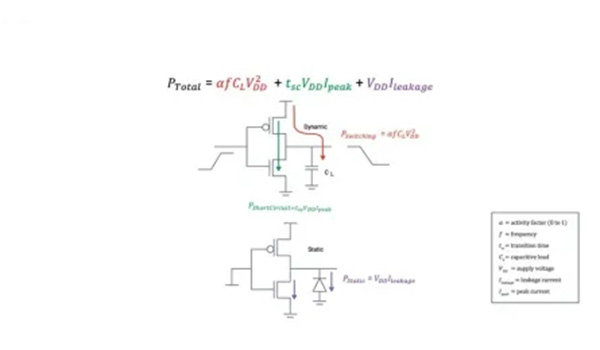

低功耗設計的目標是減少集成電路(IC)的整體動態和靜態功耗,這是實現下一代應用的關鍵方面。這個過程涉及到減少動態和靜態功耗。動態功耗包括開關和短路功率分析,而靜態功耗主要包括泄漏電流分析。包含上述三種貢獻的功率方程如圖1所示。

圖1

在IC制造工藝基于90nm到16nm技術的那些年,設計師的注意力集中在減少泄漏功耗上,因為它比動態功耗(10%到15%)所占比重更大(85%到95%)。隨著從16nm到14nm的過渡,功率方程發生了變化;泄漏功耗得到了很好的控制,而動態功耗變成了一個更重要的問題。這主要是由于從平面晶體管架構過渡到FinFET晶體管架構,一種在襯底上構建的多柵器件,其柵極位于通道的兩側、三側或四側,或包裹在通道周圍,形成雙柵甚至多柵3D結構。

在未來幾年,電子制造領域的不斷進步將導致7nm、5nm甚至3nm的制造工藝,再次突顯泄漏功耗的重要性。

AI的新挑戰

AI在電子應用中的日益普及引入了新的功率挑戰。性能、功率和面積(PPA)范式仍然是設計師要實現的目標。不同的是,隨著AI芯片的引入,最大化功率變得更加困難而不犧牲功率。如今,性能實際上受到功率的限制,并且在不擔心散熱和熱管理的情況下很難可靠地將功率傳遞到芯片的每個部分。

定義為SoC在實際系統中工作時所見的現實活動的向量質量,對于動態功率分析和優化至關重要。

“最大的問題是估計工作負載,特別是當SoC在實際系統中運行時,”Synopsys設計組的低功耗架構師兼研究員Godwin Maben說。“我們需要知道工作負載來測量和優化動態功率。涉及到AI時,沒有預定義的基準。我們需要識別這些工作負載,確保它們被捕獲并盡早調試功率。”

低功耗設計意味著要理解功率在軟件開發、硬件設計和制造過程中的影響。這不是一個單步活動,應貫穿整個芯片設計過程,旨在減少整體動態和靜態功耗。

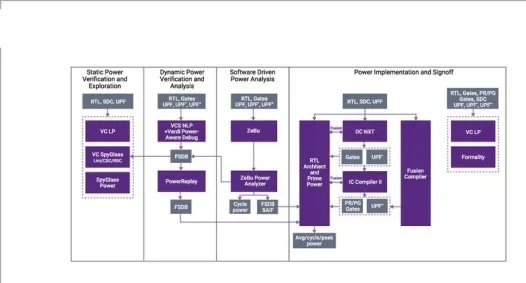

如圖2所示,設計和驗證方法分為五個主要階段:

靜態功率驗證和探索

動態功率驗證和分析

軟件驅動的功率分析

功率實現

圖2

仿真的作用

提供SoC功耗估算是一項艱巨的任務,要求設計師設置能夠盡可能真實地再現實際工作條件的測試臺。能夠滿足這些要求的最佳系統是仿真。

為AI芯片運行功率分析需要適當的工具,能夠獲取和處理數百GB、包含數十億或數萬億的時鐘周期。仿真系統中的功率分析有助于解決這個問題,因為它可以僅識別功率分析的感興趣窗口。

“AI芯片引入了兩個新概念,”Maben說。“第一個是驗證調試具有挑戰性,因為它需要很長時間。第二個是如何開發應用軟件,以便在芯片啟動時可以準備就緒。這就是仿真和原型設計概念出現的地方。”

得益于其獨特的快速仿真架構、最先進的商業FPGA和基于FPGA的仿真軟件創新,Synopsys的ZeBu服務器是業界最快的仿真系統,提供了傳統仿真解決方案2倍的性能。ZeBu軟件為用戶提供了有價值的工具,如快速編譯器、先進的調試(包括與Verdi的本地集成)、仿真加速、混合仿真和功率分析。

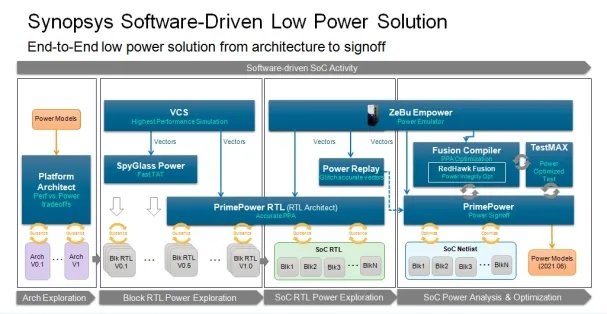

當應用程序在仿真器上運行時,它最終會被轉換為SoC的向量。這些向量可以用來運行仿真,從而驗證芯片在仿真器中的功能。仿真是獲取工作負載的正確平臺,因為它生成了用于功率分析優化的目標向量。如圖3所示,ZeBu EmPower向量由PrimePower RTL使用,為設計師提供有用的信息。

圖3

AI芯片使用了許多數學函數,主要是乘法和矩陣操作,這些操作由專用和優化的組合邏輯執行。

“當我們進入這些計算密集型應用時,設計師擔心的新概念是低幾何尺寸下的毛刺功率,”Maben說。“毛刺功率占總功率的25%以上,并且我們知道毛刺功率意味著功率浪費。”

毛刺的數量與SoC執行的操作數量成正比,使毛刺成為需要解決的AI加速器的重要問題。毛刺有兩種類型:慣性毛刺和傳輸毛刺。慣性毛刺可以通過架構解決,而傳輸毛刺是由于邏輯單元的延遲,導致邏輯門輸入的到達時間不同。毛刺正成為一個非常大的話題,因為它們非常難以優化和測量。

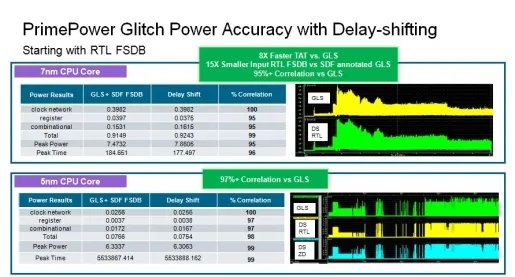

圖4

Synopsys提供了端到端的RTL到門級毛刺功率分析和優化解決方案。在RTL階段,PrimePower RTL(見圖4)可以計算并報告每層次的毛刺,并且可以指向生成最高毛刺水平的RTL源代碼行。PrimePower解決方案還提供了使用RTL仿真的延遲/毛刺感知向量生成,并且可以使用零延遲門級仿真或定時感知仿真執行毛刺功率分析,與SPICE功率數值緊密相關。

浮思特科技專注功率器件領域,為客戶提供IGBT、IPM模塊等功率器件以及MCU和觸控芯片,是一家擁有核心技術的電子元器件供應商和解決方案商。