新聞資訊

新聞資訊 知識專欄

知識專欄由于 mosfet 在電源管理設計中提供關鍵的開關功能,因此選擇具有物理、熱和電氣屬性優化平衡的器件對于提高功率密度至關重要。功率 MOSFET 封裝的最新創新提高了性能,并以極其緊湊的外形提供了堅固性。

導通電阻最小化

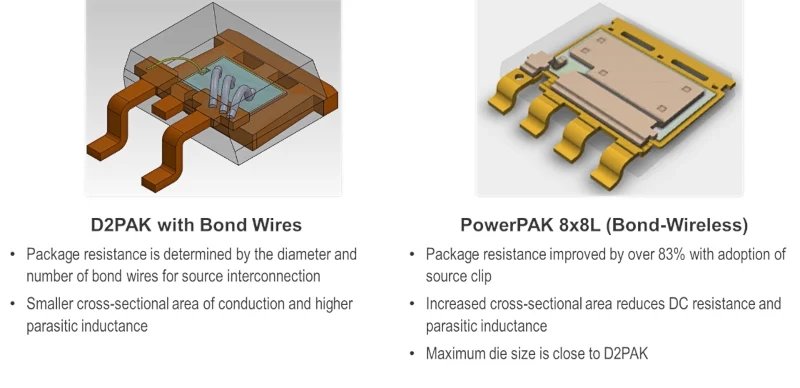

傳統晶體管外形 (TO) 封裝為需要數百瓦至數千瓦額定功率的動力系統應用提供了經過驗證的解決方案。采用 TO 封裝的產品通常使用鋁 (AI) 線將MOSFET硅的“源極”連接 到端子。這種類型的結構有其局限性,特別是對于 R DS面積非常低的最新技術而言。

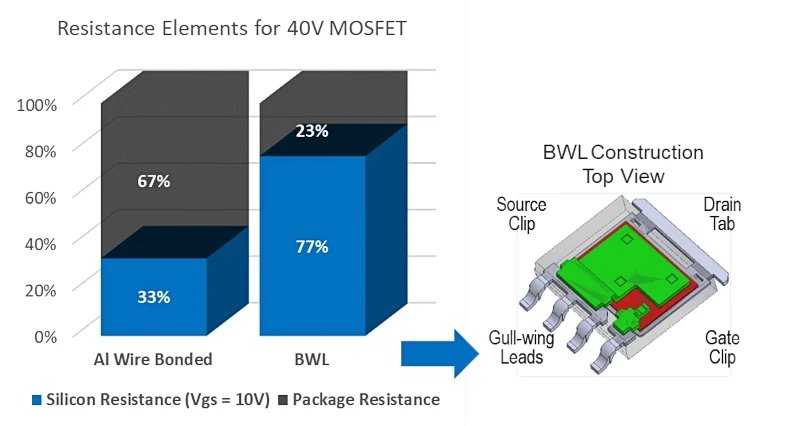

例如,采用鋁線的 7 引腳 D2PAK 中最先進的 40 V 器件的硅電阻和封裝電阻之間的比例為 33% 至 67%。因此,固有的限制阻礙了更好的MOSFET產品的創造。

隨著半導體行業不斷減少 R DS技術領域,封裝也需要創新以更好地補充硅。新的封裝結構用用于表面貼裝封裝的無線鍵合 (BWL) 互連取代了鋁線。在 BWL 架構中,MOSFET 的源極和柵極通過兩個金屬夾連接到端子。這種雙夾結構通過有限元分析進行了優化,以減少芯片和引線上的應力,同時最大限度地減少電阻和電感。

源極夾有效擴大了傳導電流的橫截面積,使封裝電阻低至 0.1 mΩ,從而將封裝對總電阻的貢獻降低至 23 % 或更低。結合最新的硅片,低壓器件可以輕松實現 微歐姆范圍內的R DS(ON) 。

金屬源夾還充當散熱片,以改善封裝的熱傳遞。此外,用于 BWL 封裝的晶圓被研磨至 50 μm 厚,以實現更低的 R DS(ON) 和卓越的熱性能。

提高性能和效率

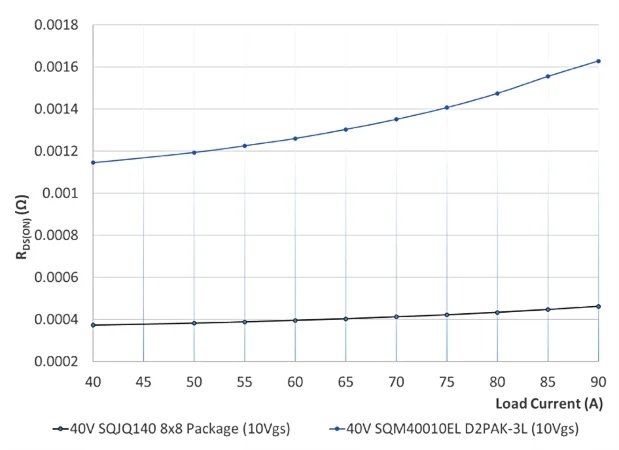

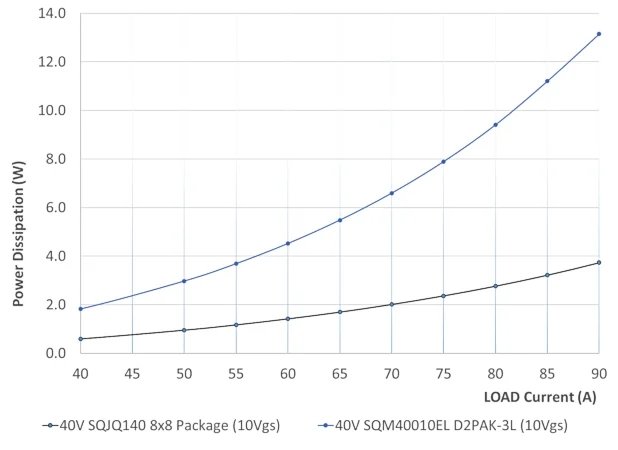

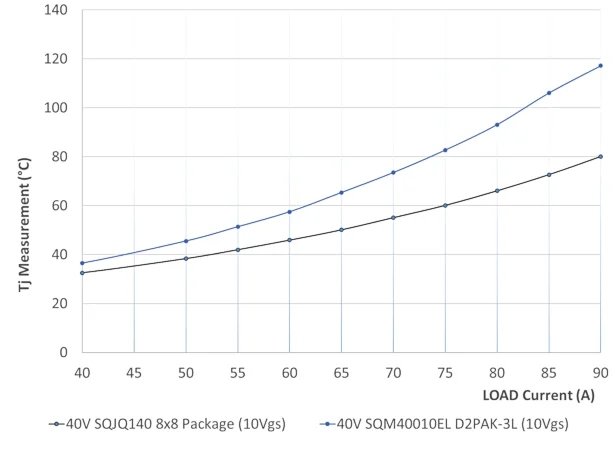

由于 P = I 2 *R,給定電流 (I) 的傳導功率損耗 (P) 可以通過具有較低的 R DS(ON) 值來降低。隨著功率損耗使結溫升高,R DS(ON)也會隨著器件變熱而升高。降低功率損耗可以使 BWL 封裝中的器件保持較低溫度,并防止 R DS(ON) 隨著負載電流的增加而快速增加。

由于 BWL 結構最大限度地降低了整體電阻,因此采用 8 mm x 8 mm 封裝的最佳 40 V 器件比我們產品組合中最佳的 D2PAK 產品溫度低 40°C。此外,更小的封裝占用更少的 PCB 空間,有助于實現更高的功率密度。

對于液泵或動力轉向系統等動力系統應用,較低的傳導損耗意味著較低的工作溫度,并降低熱管理系統的復雜性以節省成本。

PCB 占地面積減少并增強板級可靠性

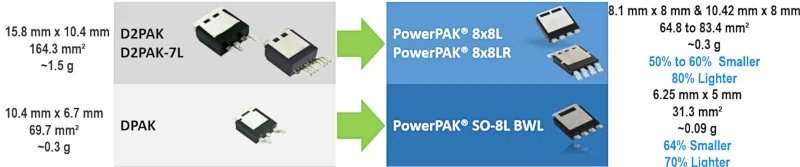

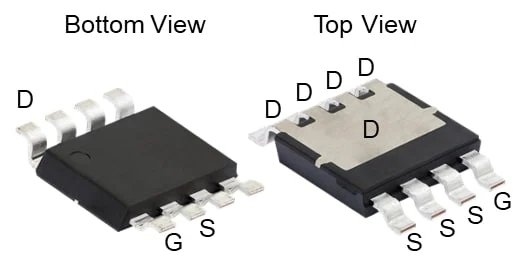

BWL 結構目前適用于各種表面貼裝封裝類型,包括 PowerPAK 8x8L、8x8LR、SO-8L 和 1212-8SLW。這些封裝在底部或頂部均有裸露的漏極焊盤,以實現更好的熱傳遞。這些封裝的典型占位面積范圍從 8x8LR 的 80.34 平方毫米到 1212-8SLW 的 10.89平方毫米。

與傳統 TO 封裝相比,使用 PowerPAK 封裝進行設計需要更少的 MOSFET PCB 空間。千瓦級以上的高功率應用通常需要多個大型芯片 MOSFET,例如 D2PAK。這些 TO 封裝的尺寸至少為 160 mm 2 ,并聯配置時會占用大量電路板空間。相比之下,PowerPAK 8x8L 的占地面積僅為 64.8 mm 2。當 PCB 上放置數十個器件時,小尺寸和較輕封裝重量的優勢變得更加顯著。

頂部冷卻的 PowerPAK 8x8LR 的封裝尺寸稍大,為 83.36 mm 2,并且該封裝比 D2PAK 占用的 PCB 空間少 50%。封裝頂部暴露的排水墊允許熱量直接向上遷移到散熱器或外殼。

新型 PowerPAK 的一大顯著特點是其鷗翼形引線,其設計目的是最大程度地消除應力和實現卓越的板級可靠性。在開發階段,封裝經過嚴格的老化和壓力測試,例如測試板上的功率溫度循環或振動測試。用于封裝的專有模塑料具有定制特性,可最大限度地減少 CTE 不匹配并減少熱循環產生的應力。鷗翼式引線經過精心設計,可最大程度地消除機械應力。因此,該封裝旨在實現高板級可靠性并可降低退貨率。

頂部冷卻封裝

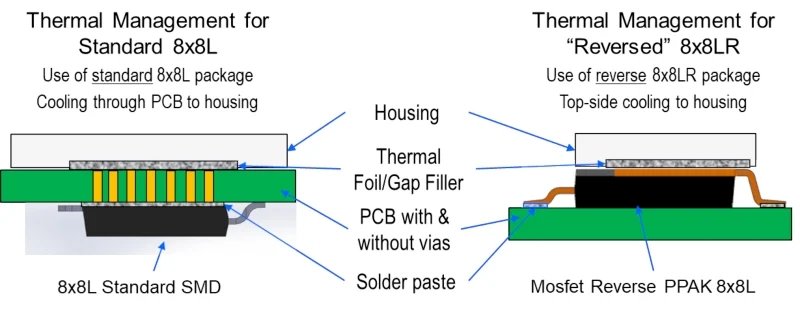

選擇在高電流下運行的動力系統應用通常需要利用金屬外殼或散熱器來消除組件功率損耗產生的熱量。為了利用這種熱管理設計,理想的 MOSFET 應具有低熱阻接口以滿足散熱器的要求。一種解決方案是最新的 PowerPAK 8 x 8 LR 封裝,它提供頂部冷卻功能并針對散熱進行了優化。

漏極焊盤位于封裝頂部,提供從封裝頂部到散熱器的直接熱路徑,界面處具有導熱膏或間隙填充物。熱量可以向上逸出至散熱器并遠離 PCB。由于主要的熱路徑是散熱器,因此 PCB 處理的熱傳遞較少,并且可以使用更小的元件,從而最終降低 PCB 成本。由于散熱器更有效地帶走熱量,系統運行溫度更低,并且能夠以更高的功率密度運行。

對于大多數漏極位于底部的 MOSFET 封裝,熱量將通過漏極焊盤推入 PCB 并消散至散熱器。該路徑包括幾種串聯的熱阻材料。MOSFET 的 PCB 區域還需要通孔以實現熱傳遞。

反向封裝還具有鷗翼引線,旨在最大程度地緩解應力。引線的靈活性允許在熱應力和機械應力的情況下發生膨脹和收縮。雖然該封裝的導通電阻低至 0.54 mΩ(8 x 8 LR,V DS = 40 V),但整體結構堅固耐用,可實現高板級可靠性,從而最大限度地減少現場回報。

要點——更小、更堅固、更節能

采用 BWL 結構的新型 PowerPAK 封裝發揮了硅的最佳性能,并且比同類 TO 封裝的器件重量更輕。由此產生的產品提高了效率并實現了更高的功率密度,因此汽車電子系統 可以更加節能。新 PowerPAK 系列的優點包括:

PCB 空間顯著減少

封裝貢獻的電阻最小化,總 R DS(ON) 在微歐范圍內

針對散熱進行優化的頂部冷卻 PowerPAK,可進一步減小 PCB 整體尺寸

鷗翼形引線設計提高了板級可靠性,延長了產品使用壽命并減少了故障機會

PowerPAK 封裝系列具有更好的電氣特性和耐用性,可提高功率密度并增強設計的可靠性。

浮思特科技深耕功率器件領域,為客戶提供IGBT、IPM模塊等功率器件以及MCU和觸控芯片,是一家擁有核心技術的電子元器件供應商和解決方案商。