新聞資訊

新聞資訊 知識專欄

知識專欄金屬氧化物半導體場效應晶體管 (mosfet) 可能是 20 世紀最引人注目的電子成就。第一個商用 MOSFET 電路出現于 1964 年,因其封裝密度高、功耗小、成本低而廣受歡迎。集成電路于1958年推出,互補MOS(CMOS)技術于1967年推出。第一個商業化生產的微處理器是英特爾公司于1971年發布的Intel 4004。它開始了一場小型化和性能改進的競賽。

隨著制造工藝的進步,晶體管和柵極變得越來越小,效率也越來越低。規模化帶來了許多新問題。隨著器件尺寸的減小,短溝道效應、可變性、量子隧道泄漏和遷移率下降帶來了關鍵的困難。

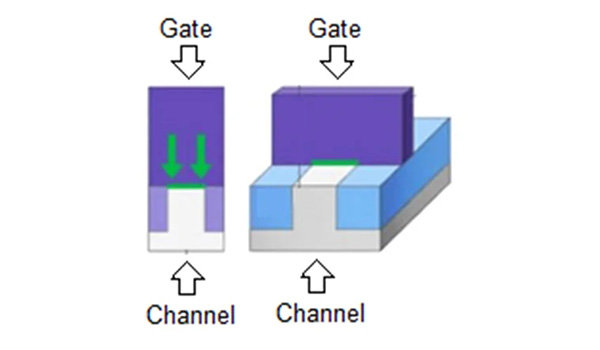

解決這些問題的一種方法是發展為三維配置,通道的柵極位于三個側面,從而提供更多的表面積來控制靜電。工程師們考慮了鰭形 FET 等多柵極器件,使我們所熟知的 FinFET 晶體管成為現實。

這種方法有很多好處——更少的漏電流、增強的驅動電流、更快的開關時間和卓越的可擴展性——改善通道的控制,同時減小晶體管的整體尺寸。柵極表面可以保持或增加——漏電流和其他短溝道問題重新得到控制。

當技術從 22nm 發展到 16nm 時,許多半導體制造公司從平面晶體管轉向 FinFET 晶體管。

2009年9月22日,英特爾在英特爾開發者論壇上展示了一款22納米晶圓。該單元的尺寸是當時最小的SRAM。英特爾首次使用其 3D Tri-Gate 工藝。

但FinFET也有局限性,在最近兩代已經出現了疲憊的跡象。在 3nm 及以上工藝節點,FinFET 可能無法再正確控制漏電流和其他短溝道效應,需要新技術來繼續進一步縮小尺寸。

采用 FinFET 的最新節點技術的成本降低速度有所放緩。這一事實降低了大規模生產中擁有先進節點技術的公司數量。

現在,業界的半導體公司和代工廠面臨著一場新的晶體管革命。

晶體管的演變

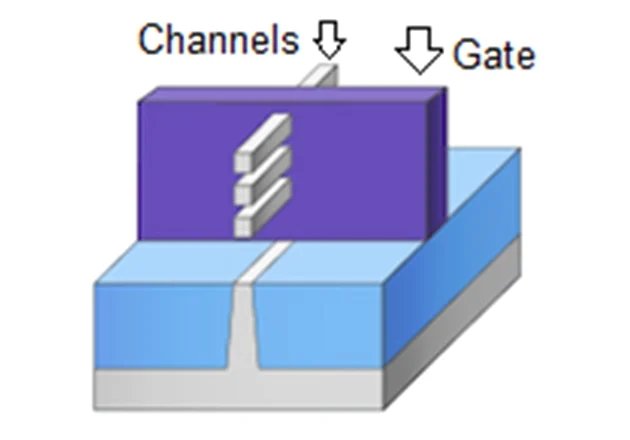

FinFET 是一項有有效期的技術。過去十年中,后 FinFET 晶體管研究正在評估從圍繞通道三側的柵極到完全包圍通道的柵極(類似于被管狀柵極包圍的圓柱形通道)的演變。這種布置是采用納米線或納米片的全柵 FET 或 GAAFET。與 FinFET 或平面晶體管相比,這種設計的構建難度更大。納米線和納米片技術目前正在進行中,可以提高通道并允許其寬度根據需要縮放。

三星邁出了第一步,將自己定位為在 3nm 制造工藝中展示多橋通道 FET 或MBCFET技術的領導者。該技術集成了新型全柵晶體管作為主要創新。

新的三星晶體管是納米片。堆疊是垂直的,水平的納米片,就像一疊打印紙,取代了傳統的翅片。

與 FinFET 相比,三星突出了三個優勢:

不需要額外的區域來提高速度。納米片垂直堆疊,而不是添加平行翅片。

預計 MBCFET 將能夠取代 FinFET,而無需改變設備占用空間的尺寸或配置。

支持與 FinFET 相同的工藝工具和制造方法,降低成本并加速實施。

由于 GAAFET 晶體管仍處于測試階段,我們無法宣布最終的性能或效率改進。三星估計,在相同的3nm光刻工藝下,數字是節能50%、性能提升30%、面積減少45%。

這些高數字無疑標志著實現它的芯片的前后變化。回顧從平面到 FinFET 的跨越,我們可以說這些數字是可信的。

三星最初的計劃是在 2021 年實現量產,并在 2022 年進入市場。但是,他們最近宣布由于 COVID-19 危機而導致一些延遲。

其他半導體廠商如英特爾或臺積電尚未正式表態。盡管如此,預計他們將盡早發布有關這項技術的公告。

英特爾仍在通過增加鰭的高度來設計 FinFET。然而,有一天,FinFET 的縮放能力將變得難以承受,最終將迫切需要使用新技術來維持縮放。

英特爾發言人最近給出了線索,表示他們預計在不超過五年的時間內生產出GAAFET。

臺積電在 3nm 制程技術上將繼續采用 FinFET。他們承認自己有能力更新 FinFET,以允許通過工藝節點的另一次迭代進行擴展。臺積電還利用 FinFET 的可預測性來遵守其批準的時間表。

臺積電、英特爾和三星都將尋求保持最佳 3 納米和 5 納米光刻工藝的領先地位。

FET 的未來

超大規模集成電路(VLSI)電路使移動設備的普及成為可能——在最小的面積內塞滿了數十億個晶體管——加入了提高計算能力和能源效率的需求。

智能手機、增強現實和虛擬現實 (AR/VR) 以及物聯網 (IoT) 等始終處于待機狀態的設備需要超低功耗系統,這使得業界不斷尋找更好的晶體管。

許多 CMOS 晶體管的替代品正在研究中。添加柵極來生產全柵極晶體管可能是控制超大規模通道中靜電的最終解決方案。垂直堆疊通道的選擇可以是傳統 CMOS 縮放的最大程度。令人興奮的是發現誰在競爭中領先不再是節點的密度和性能,而是面積的減少和能耗。浮思特科技深耕功率器件領域,為客戶提供IGBT、IPM模塊、MODULE等功率器件,是一家擁有核心技術的電子元器件供應商和解決方案商。